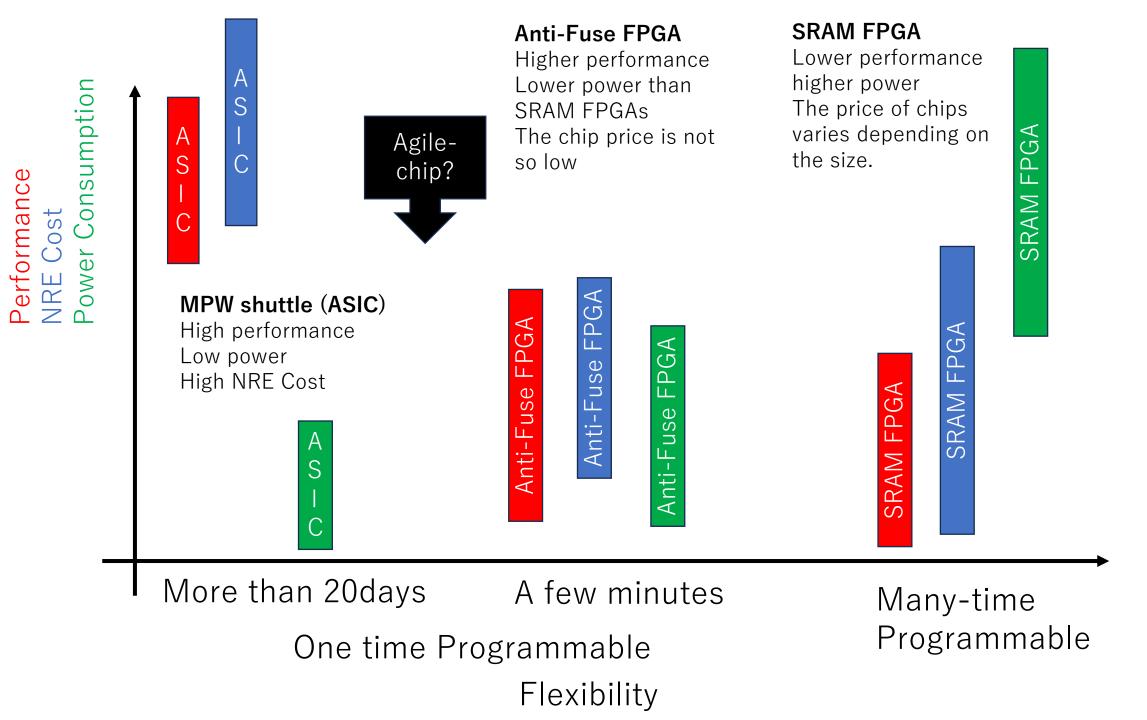

# Can the Agile-chip platform carve out a niche between ASICs and FPGAs?

Hideharu Amano, Atsutake Kosuge, Hirofumi Sumi, Naonobu Shimamoto, Yukinori Ochiai, Yurie Inoue, Tohru Mogami, Yoshio Mita, Makoto Ikeda System Design Lab,

Graduate School of Engineering, The University of Tokyo, Tokyo Japan

CoolChips28

MEXT(Ministry of Education) Initiatiated to Establish Next-generation Novel Integrated Circuits Centers (X-NICS)

To promote the formation of core academic centers for R&D and human resource development that leverage Japan's strengths, with the aim of creating innovative semiconductor LSI that will play an important role in achieving a carbon neutral 2050 and digital society, as well as ensuring economic security.

- "Agile-X Democratization Base of Innovative Semiconductor Tech", Univ. of Tokyo

- ➤ "Green-niX Res. And Education Base", Titech

- "Spintronics X Semiconductor Res. Hub", Tohoku Univ.

- Agile-X platform for TAT: 1/10, Cost: 1/10

- x10 LSI designers and make LSI democratize

#### Agile-X enables quick and low-cost chip development

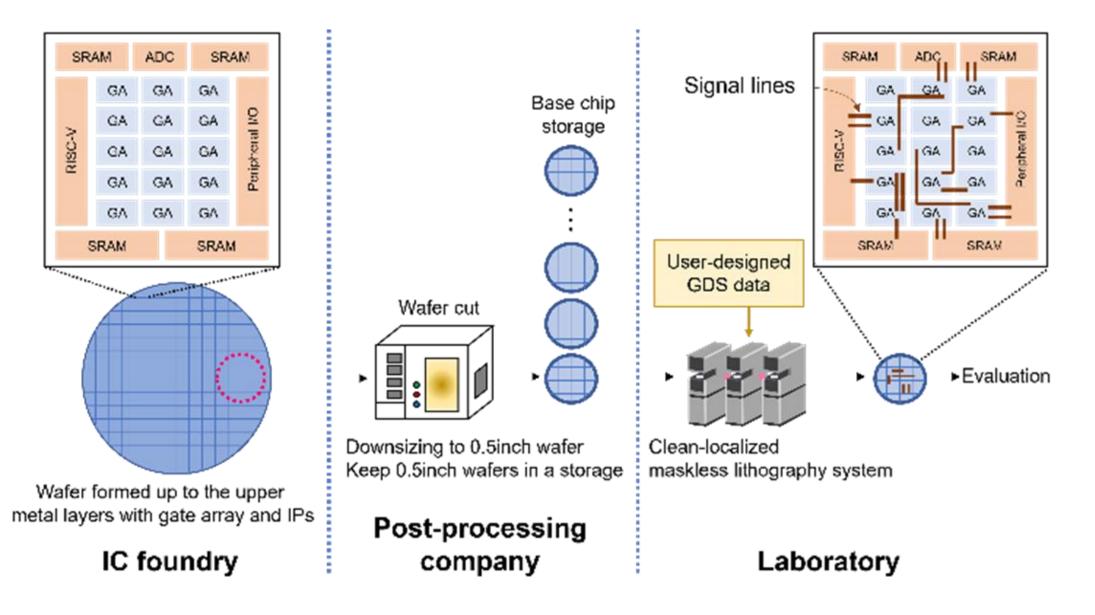

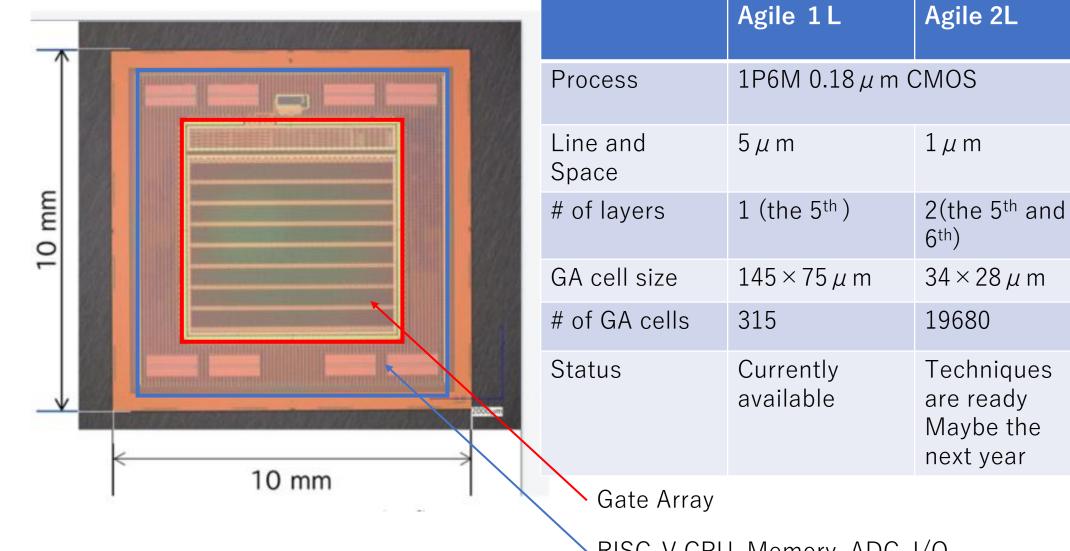

### The current status of Agile-Chip

RISC-V CPU, Memory, ADC, I/O

#### Evaluated Chips and Applications

| Evaluated Chips                  | MPW shuttle<br>(ASIC)                      | Agile-chip<br>Platform                     | Polarfile Anti-<br>fuse FPGA                      | Zunq<br>Ultrascale+<br>SRAM FPGA |  |  |  |

|----------------------------------|--------------------------------------------|--------------------------------------------|---------------------------------------------------|----------------------------------|--|--|--|

| NRE Cost (\$)                    | 89.6K                                      | 22.2                                       | 422                                               | 341                              |  |  |  |

| Programmability                  | One-time                                   | One-time                                   | One-time                                          | Many-time                        |  |  |  |

| Process<br>(Programming)<br>time | More than 20<br>days                       | 30 mins                                    | A few mins                                        | a few mins                       |  |  |  |

| Process                          | $0.18\mu\mathrm{m}1\mathrm{P6M}$           | $0.18\mu\mathrm{m}1\mathrm{P6M}$           | 22nm                                              | 16nm                             |  |  |  |

| Tool                             | Synopsys Design<br>Compiler<br>2023.12-SP2 | Synopsys Design<br>Compiler<br>2023.12-SP2 | Libero SoC<br>v2024.2 (Service<br>is stopped now) | Vivado 2021.1                    |  |  |  |

| Application                      |                                            |                                            |                                                   |                                  |  |  |  |

| CRC checker                      | 8-bit Cyclic Rec                           | 8-bit Cyclic Redundancy Code Checker       |                                                   |                                  |  |  |  |

| DCT                              | 1-dimensional I                            | 1-dimensional DCT used in JPEG decoder     |                                                   |                                  |  |  |  |

| AES                              | Advanced Encry                             | Advanced Encryption Code 128 encoder       |                                                   |                                  |  |  |  |

| FPC                              | Frequent Patte                             | Frequent Pattern Compression decoder       |                                                   |                                  |  |  |  |

| sXXX                             | ISCAS benchma                              | ISCAS benchmark from IWLS 2005             |                                                   |                                  |  |  |  |

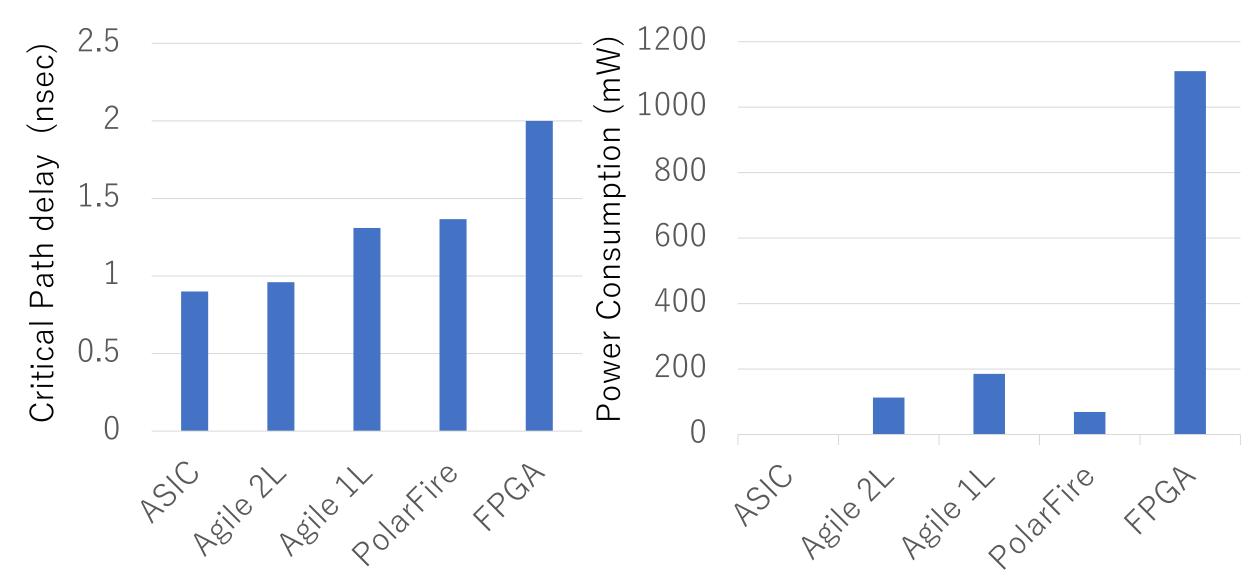

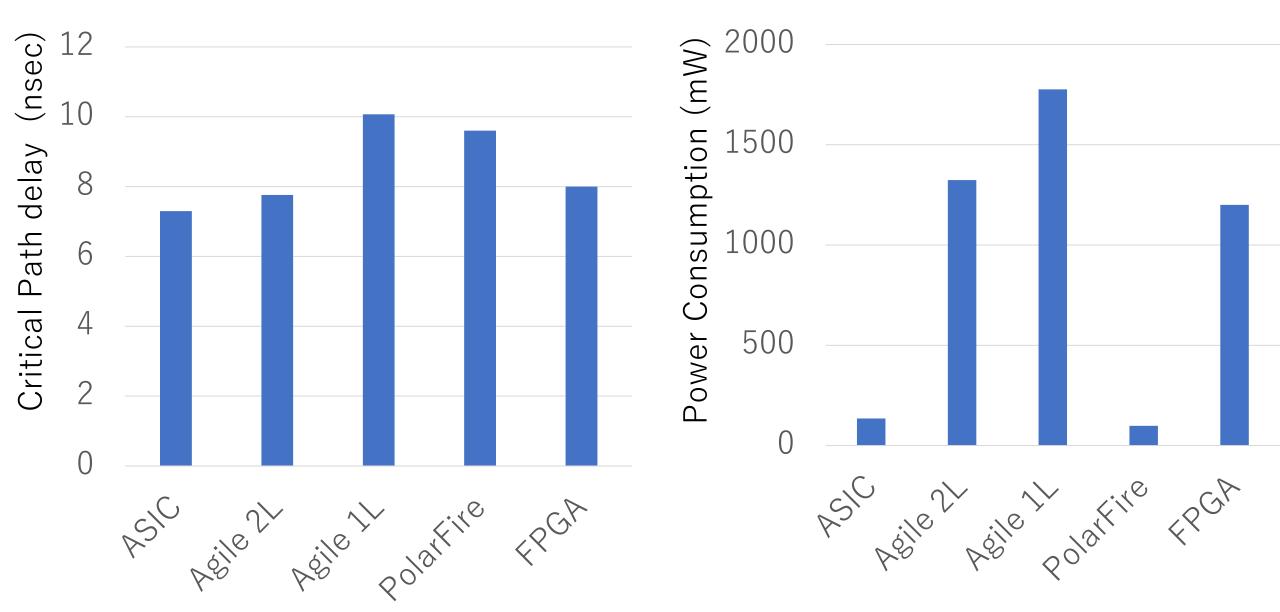

#### CRC checker

Agile 2L is better than Polarfire and SRAM FPGA in terms of performance. Polarfire appears to reduce power consumption at the expense of performance. DCT

FPGAs with DSP modules are advantageous. Agile 1L is the worst, while Agile 2L is competitive.

#### Performance and power for other applications

|                | ASIC  | Agile 2L | Agile 1L | FPGA  |

|----------------|-------|----------|----------|-------|

| AES delay(ns)  | 3.24  | 4.01     | 7.27     | 7.14  |

| power (mW)     | 59.6  | 954      | 910      | 1166  |

| FPC delay(ns)  | 3.25  | 4.51     | 6.45     | 4.242 |

| power (mW)     | 50.8  | 728      | 889      | 1339  |

| s382 delay(ns) | 0.3   | 0.21     | 0.41     | 4.84  |

| power (mW)     | 0.207 | 22       | 26       | 1108  |

| s510 delay(ns) | 2.48  | 3.09     | 4.45     | 4.84  |

| power (mW)     | 0.207 | 22       | 26       | 1113  |

| s820 delay(ns) | 2.75  | 4.89     | 5.85     | 4.84  |

| power (mW)     | 0.113 | 10.5     | 16.4     | 1113  |

- Polarfire cannot be evaluated because the service has been discontinued.

- The performance of Agile 2L is better than that of FPGA, and close to ASIC.

- The performance of Agile 1L is comparable to FPGA.

- The power of Agile 1L/2L is much better than FPGA, but much worse than ASIC.

## Conclusions

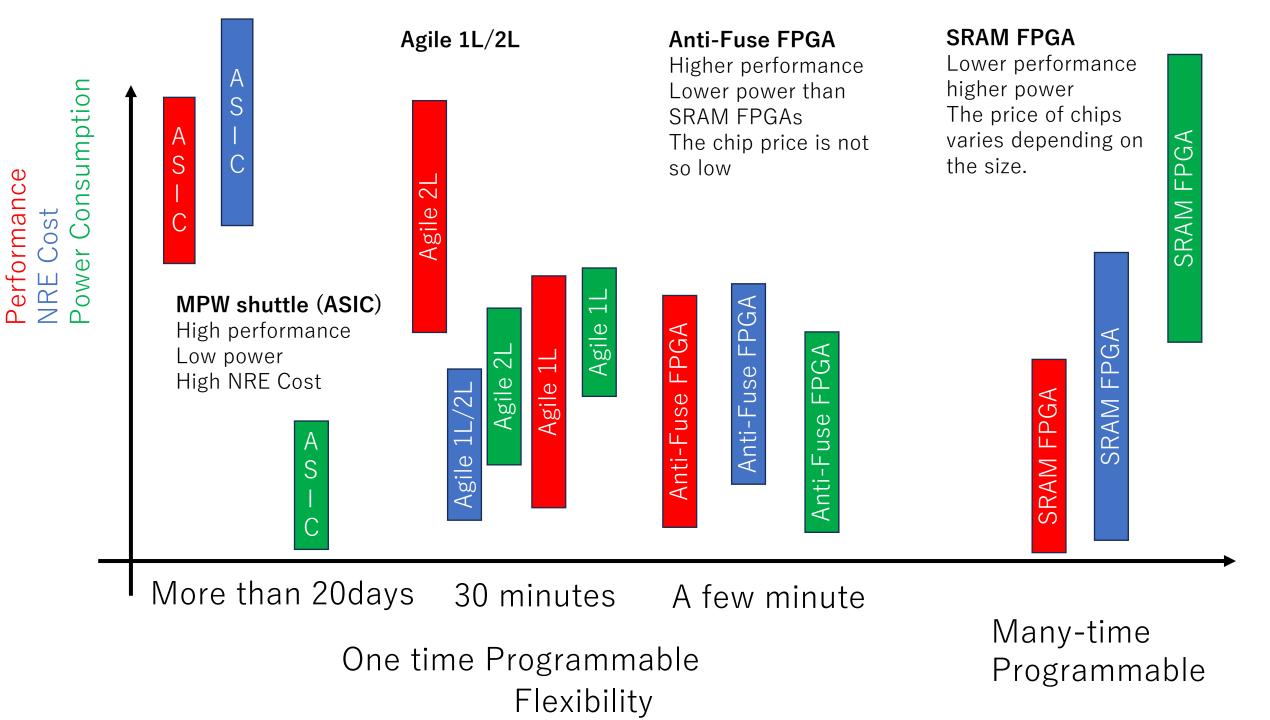

- The main advantage of Agile 1L/2L is its low cost for ultra-low-volume production.

- The main issue with Agile 1L/2L at present is the limited number of gates, but this can be improved in the future.

- The performance of Agile 2L is better than FPGAs and close to ASIC.

- The performance of Agile 1L is comparable to that of FPGAs in the application without DSP modules.

- Agile 2L can be used instead of anti-fuse style FPGAs, although Agile 1L is mainly for education.

- Agile chips are advantageous for applications where SRAM-based FPGAs cannot be used, such as operations under high radiation.

- The use of more advanced process is desired.