### An SoC Design and Fabrication Hands-On Educational Course Within One Week Using Structured ASIC

Hideharu Amano, Atsutake Kosuge, Hirofumi Sumi, Naonobu Shimamoto, Yukinori Ochiai, Yurie Inoue, Tohru Mogami, Yoshio Mita and Makoto Ikeda

# Why is semiconductor education difficult ?

- Recently in Japan, there has been increased investment in the semiconductor industry, such as TSMC(JASM), Micron, and Rapidus.

- However, this causes a shortage of talent.

- Few Students Aspire to Enter the Semiconductor Field

- One major reason is the lack of hands-on experience in semiconductor education. .

- Semiconductor chip fabrication experiments requires

- The high costs and time required.

- Extensive knowledge, including electronic circuits, CAD tools, and fabrication processes.

### There is a strong need for student lab programs

- Only with basic circuit knowledge

- Affordable cost

- A short period of time.

## MEXT(Ministry of Education) initiated to Establish Next-generation Novel Integrated Circuits Centers (X-NICS)

To promote the formation of core academic centers for R&D and human resource development with the aim of creating innovative semiconductor LSI that will play an important role in achieving a carbon neutral 2050 and digital society, as well as ensuring economic security.

- "Agile-X Democratization Base of Innovative Semiconductor Tech", Univ. of Tokyo

- ➤ "Green-niX Res. And Education Base", Titech

- "Spintronics X Semiconductor Res. Hub", Tohoku Univ.

- Agile-X platform for TAT: 1/10, Cost: 1/10

- x10 LSI designers and make LSI democratize

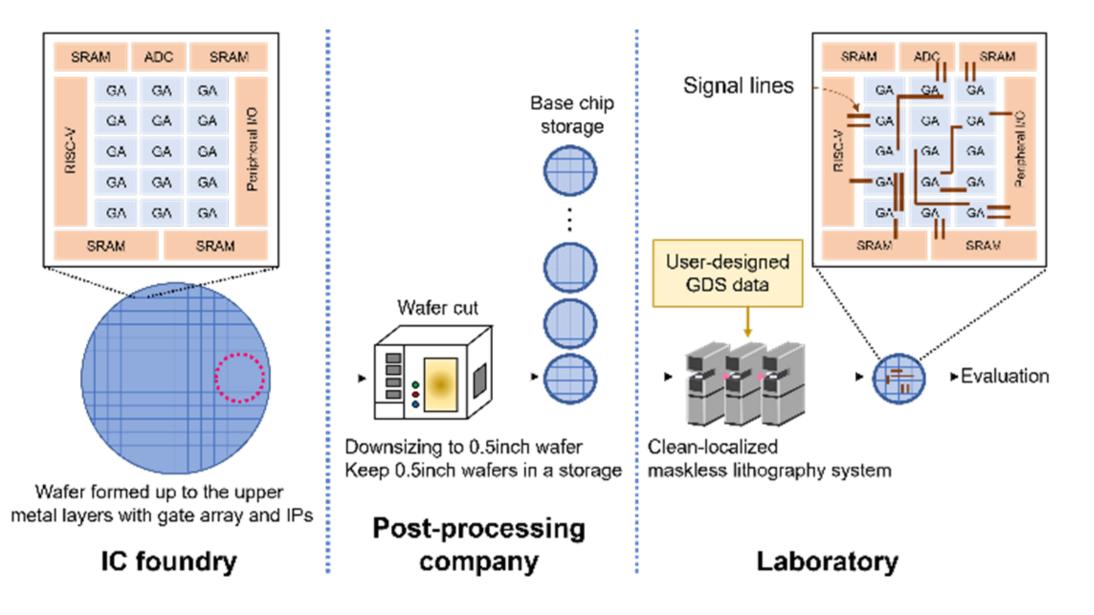

## Agile-X enables quick and low-cost chip development

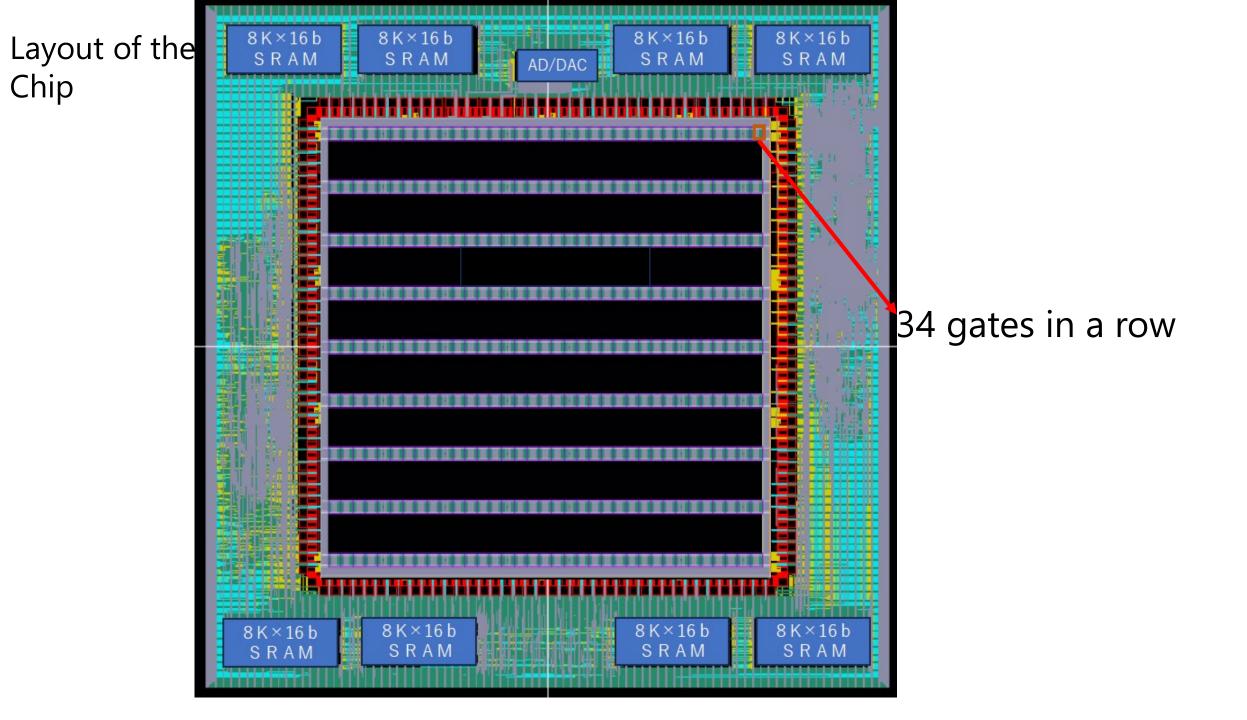

## Agile-X platform enables a quick student lab.

# Considerations

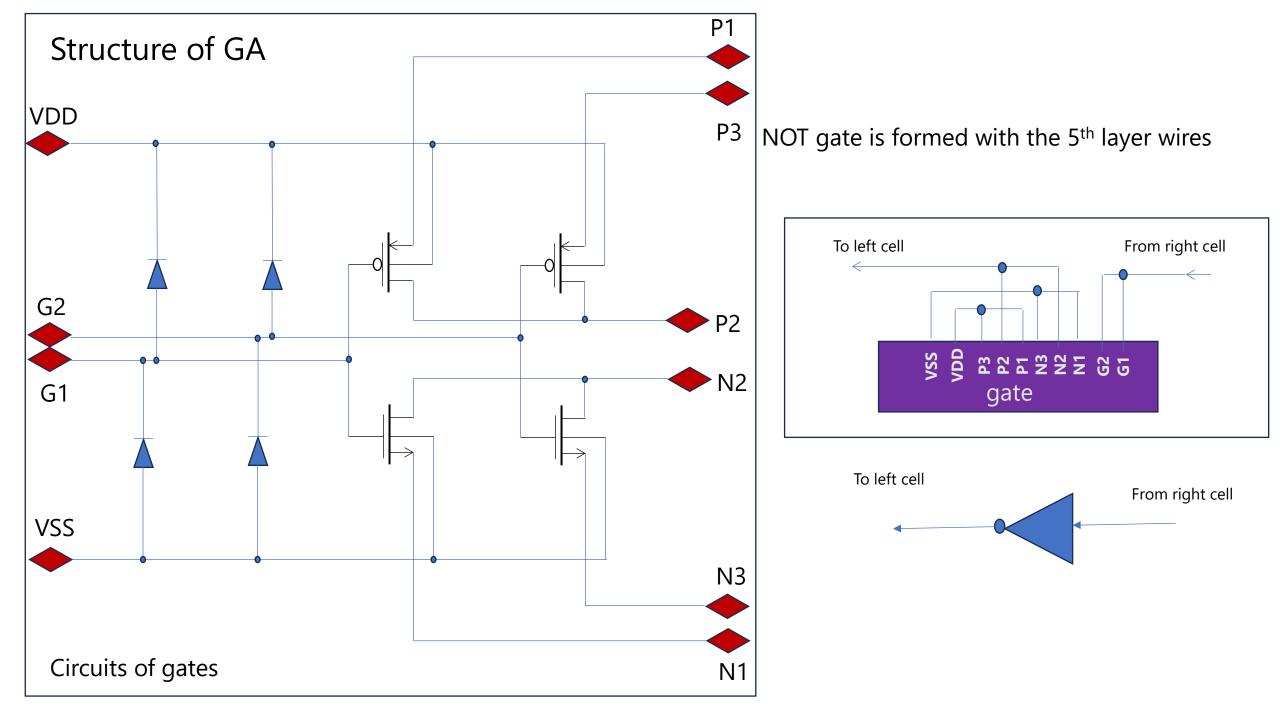

- Use a simple circuit in the GA part

- 61-stage ring oscillator

- Easy to understand with basic knowledge on electronics

- Easy to verify

- Small number of pins

- Layout with Virtuoso

- all-in-one layout tool including DRC and LVS

- Easy to make wires

- LEVIS is used for confirmation of the layout

- Students need NDA

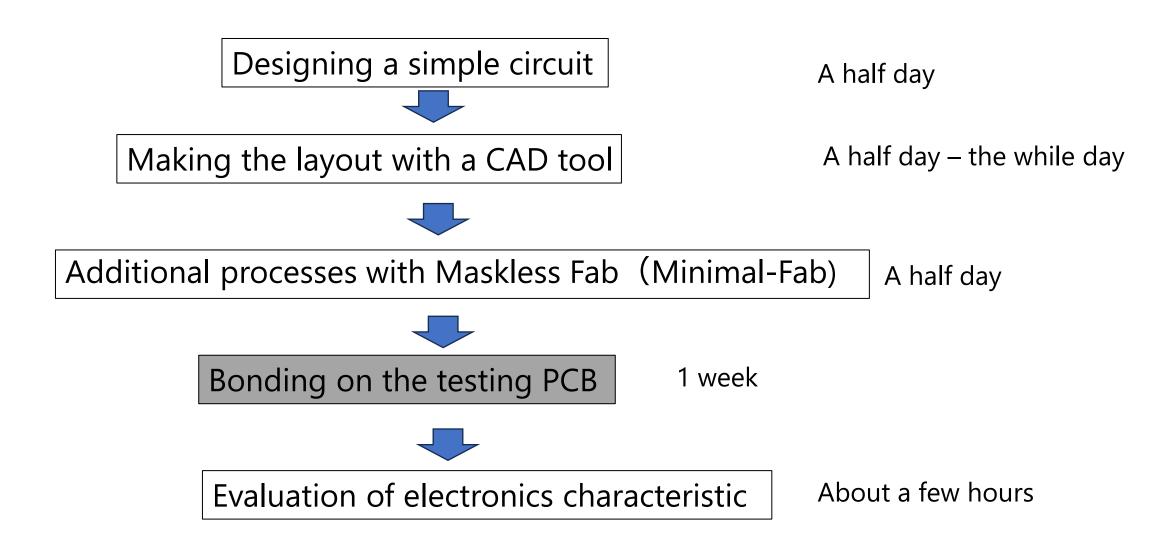

# Design flow of the student lab.

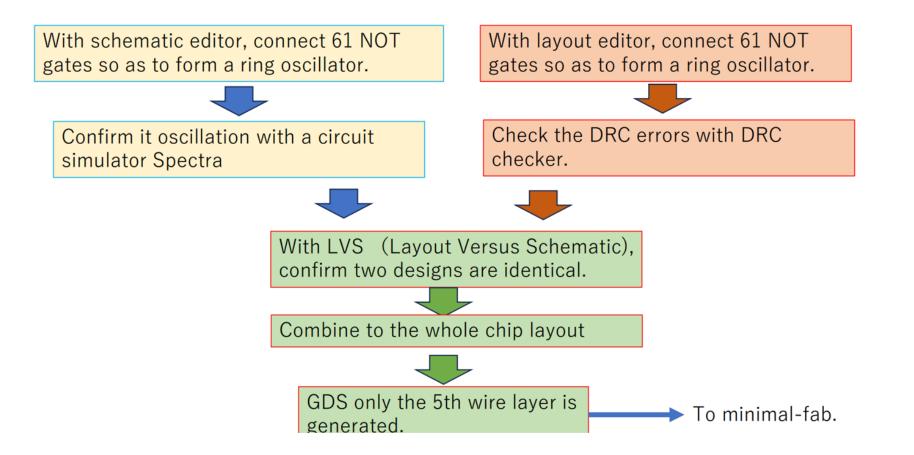

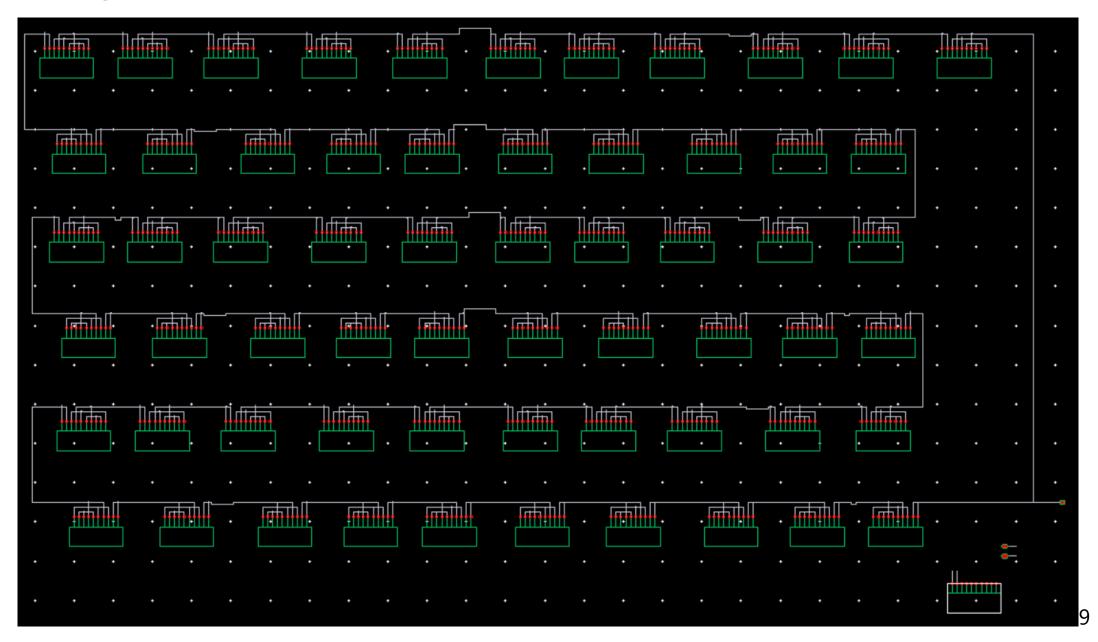

### 61-stage oscillator circuit Virtuoso circuit editor

#### Layout for ring-oscillator

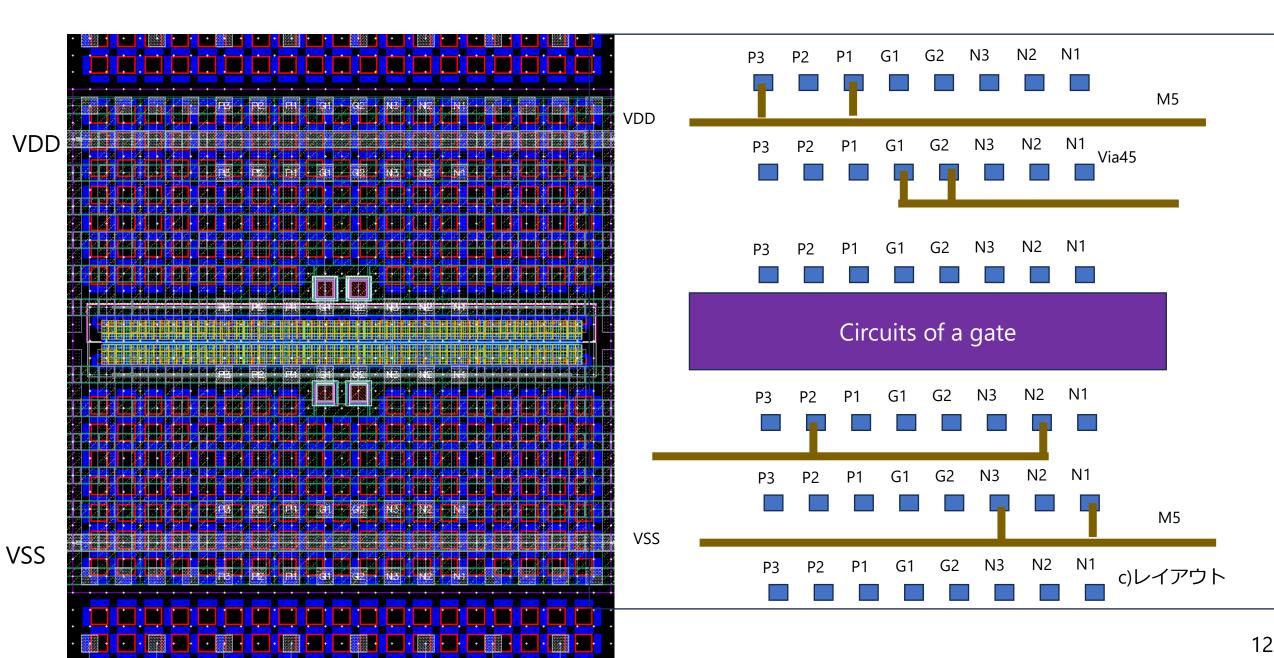

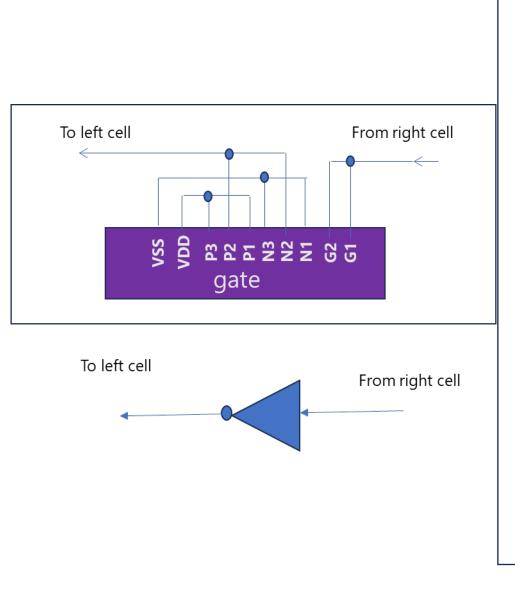

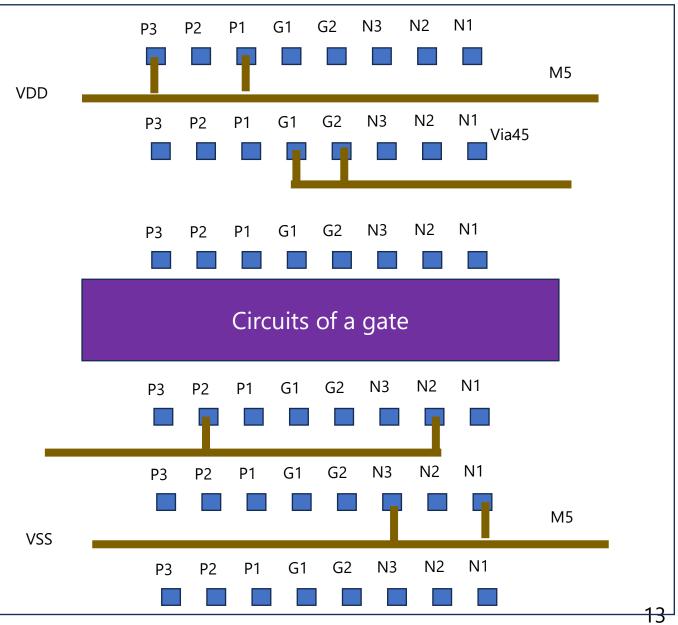

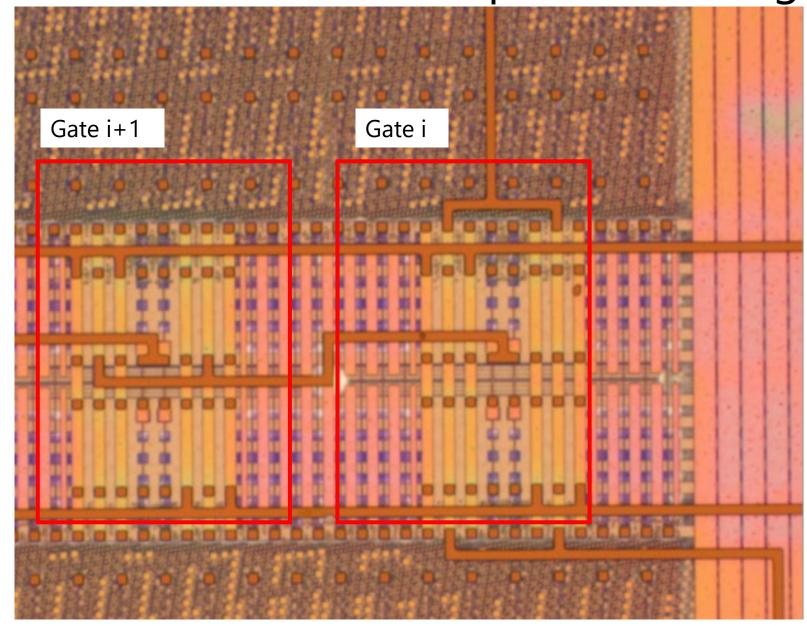

# Connection of the 5<sup>th</sup> metal layer for a not gate

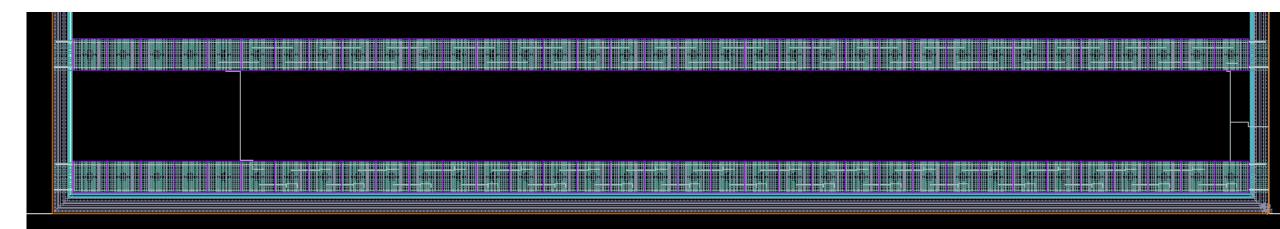

### Example of the layout 30 gates (Lower) + 31 gates (Upper)

Connect to labeled PAD ga\_out[1] is used here.

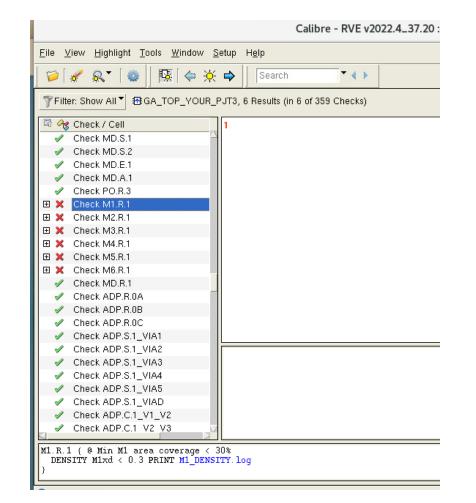

DRC check Virtuoso embedded Calibre is used.

- OK if green ✓ is shown.

- Density errors can be ignored.

- If there is no error, the layout is OK.

Virtuoso embedded LVS is used.

Circuits used for the simulation and the layout are compared.

| 4   |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

|-----|---------------------|---------------|-------|-------|------------|------|----|------|--------|-----|----------|-----|-----|----------------|---|-----|----|-----|------|-------|------|----|------|

| 4   |                     | * * * * * * * | * # # | * * * | <b>π</b> # | **   | ππ | # #  | * *    | π π |          |     | π1  | τ <del>π</del> |   | ŤΤ  | ππ |     | fπ # | f # # | ***  |    | 12   |

| 2   | **                  |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    | *    |

| 6   | **                  |               | C     | Α     | L          | I    | в  | R    | Е      |     | 1        | 5   | Y   | S              |   | r : | E  | М   |      |       |      |    | *    |

| 7   | **                  |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    | *    |

| 8   | **                  |               |       |       | L          | v    | S  |      | R      | Е   | Ρ        | 0   | I   | R              | т |     |    |     |      |       |      | #  | *    |

| 9   | **                  |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      | #  | #    |

| 0   | ***                 | * * * * * * * | * # # | ***   | ##         | **   | ## | ##   | ##     | ##  | ##       | ##  | # f | ##             | * | ##  | ## | ##  | ***  | ##    | ###  | ## | #    |

| 1   |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| .2  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| .3  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| .4  | REPORT FILE NAME:   | GA            |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| .5  | LAYOUT NAME:        |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       | т3 ' |    |      |

| . 6 | SOURCE NAME:        | GI            | A T   | OP    | YO         | UR   | P  | JT   | 3.     | sı  | c        | . n | et  | t              | ( | 'G  | A  | TC  | DP   | YO    | UR   | PJ | т3') |

| 7   | RULE FILE:          | (             | cal   | ibr   | e.         | lv   | s  |      |        |     |          |     |     |                |   |     | -  |     |      |       |      |    |      |

| .8  | CREATION TIME:      | Me            | on    | Jul   |            | 8    | 17 | : 5  | 2:     | 50  | ) :      | 20  | 24  | 1              |   |     |    |     |      |       |      |    |      |

| .9  | CURRENT DIRECTORY:  | /1            | nom   | e/u   | sr         | /h   | un | ga   | /t     | ry  | 1        |     |     |                |   |     |    |     |      |       |      |    |      |

| 0.5 | USER NAME:          | hu            | ing   | a     |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 1.1 | CALIBRE VERSION:    | v             | 202   | 2.4   | 3          | 7.   | 20 |      |        | Fr  | <b>i</b> | D   | e   | c              | 2 | 1   | 7: | 41  | 1:0  | 2     | PST  | 2  | 022  |

| 12  |                     |               |       |       | _          |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 23  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 24  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 15  |                     |               |       | ov    | ER         | AL   | L  | co   | MP     | AR  | I        | 50  | N   | R              | E | SU  | LT | 'S  |      |       |      |    |      |

| 6   |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 27  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 18  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 29  |                     | *             |       |       | **         | **   | ** | ##   | **     | **  |          | **  | **  |                | * |     |    |     |      |       |      |    | 1    |

| 0.  |                     | #             |       |       | #          |      |    | 0.0  |        |     |          | 500 |     |                | * |     |    |     | *    | -     | *    |    |      |

| 1.1 |                     |               |       |       |            |      |    | со   | RR     | EC  | T        |     |     |                |   |     |    |     |      | 1     |      |    |      |

| 12  | · ·                 |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     | 1    | '     | 1    |    |      |

| 53  |                     |               |       |       |            | **   | ** | **   | **     |     |          |     | **  |                |   |     |    |     |      | `—    | -    |    |      |

| 14  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 35  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 16  | Warning: Unbalance  | d amag        | hed   | mo    | af         | et   | q  | we   | re     |     | at       | to  | he  | ad             |   |     |    |     |      |       |      |    |      |

| 17  | Warning: Ambiguity  |               |       |       |            |      |    |      |        |     |          |     |     |                |   | a   | rb | i * | n na | ri    | 1v   |    |      |

| 18  | Warning: LVS prope  |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    | T.  |      |       | -1.  |    |      |

| 10  | Marining. Lvs prope | LUY IES       | OT    | act   | on         | . 10 | ax | -110 | - alli |     | -        | -6  | C   | 10             | a |     |    |     |      |       |      |    |      |

| 10  |                     |               |       |       |            |      |    |      |        |     |          |     |     |                |   |     |    |     |      |       |      |    |      |

| 1.7 | *****************   | ******        |       |       |            |      | ** | **   | **     | **  |          |     |     | * *            |   |     | ** |     |      |       | ***  | ** |      |

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

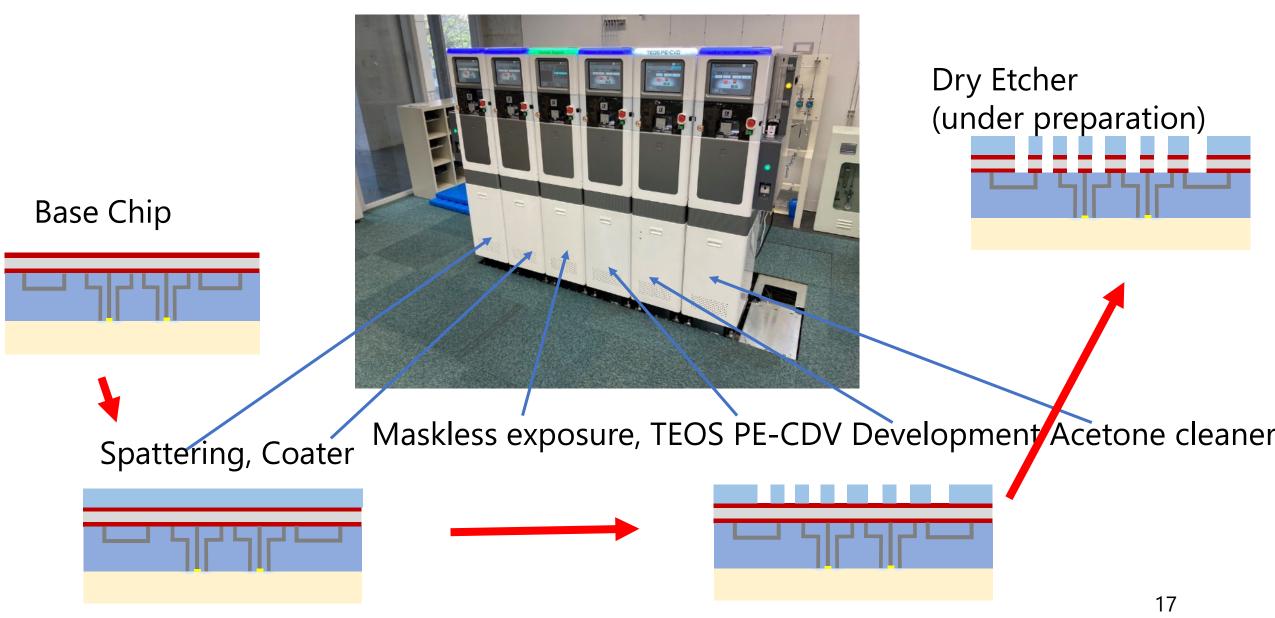

## **Processes on Minimal-Fab**

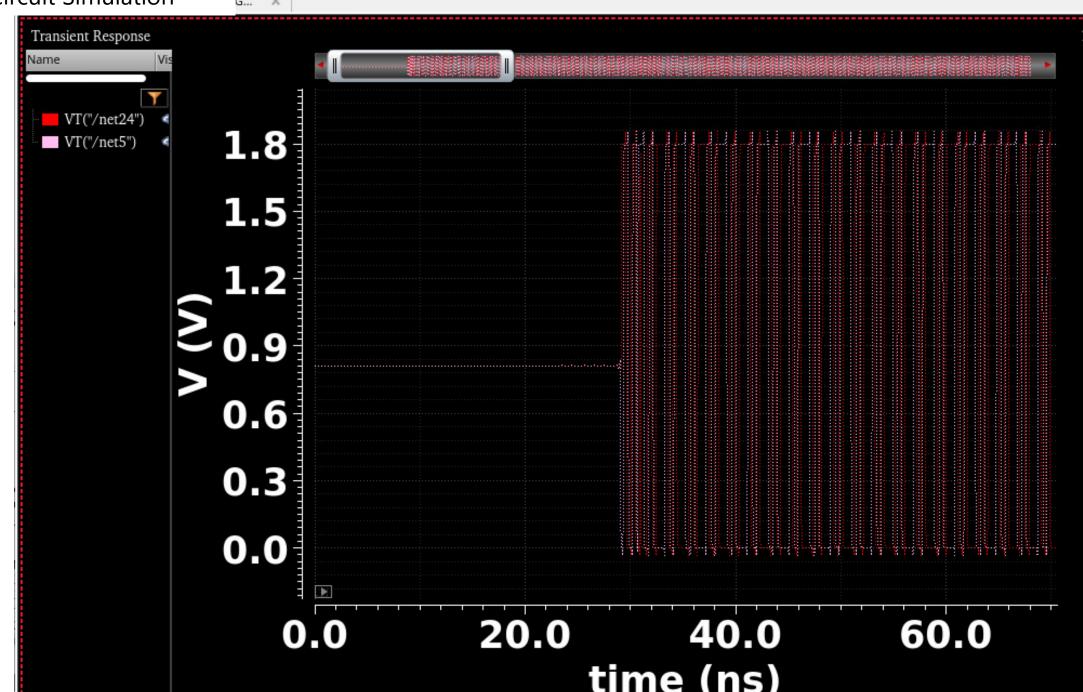

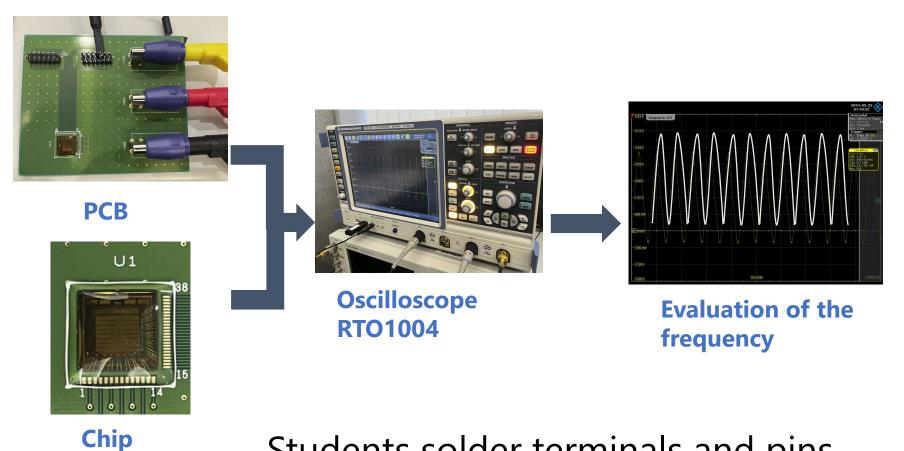

# **Circuits evaluation**

Direct bonding to the Print Circuit Board for skipping the package stage.

Students solder terminals and pins.

## Comparison of Cost and Total Process time

|                    | Full mask wafer                          | MPW Shuttle                                                                       | Our Agile-X                                                          |  |  |  |  |  |

|--------------------|------------------------------------------|-----------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| Cost amortization  | Νο                                       | By 20 designs                                                                     | By 140designs per wafe<br>By 100 base wafer                          |  |  |  |  |  |

| IPs                | RIS                                      | pheral IO                                                                         |                                                                      |  |  |  |  |  |

| Wafer cost         | 400                                      | 20                                                                                | 2.9 USD                                                              |  |  |  |  |  |

| Mask cost          | 191K                                     | 9.6K                                                                              | 13.6 USD                                                             |  |  |  |  |  |

| IP cost            | 80K                                      | 80K                                                                               | 5.7 USD                                                              |  |  |  |  |  |

| Total cost         | 271K USD<br>(1)                          | 89.6K USD                                                                         | 22.2 USD<br>(1/12252)                                                |  |  |  |  |  |

| Total process time | ~20days                                  | ~20days                                                                           | ~30min.<br>(1/960)                                                   |  |  |  |  |  |

| Assumptions        | Single design only.<br>0.18um 1P6M CMOS. | A wafer is shared with<br>20 designs.<br>IPs are not shared.<br>0.18um 1P6M CMOS. | 100 base wafer is fabricated<br>(14K base chip)<br>0.18um 1P6M CMOS. |  |  |  |  |  |

A.Kosuge, et.al. Agile-X: A Structured-ASIC Created with a Mask-less Lithography System Enabling Low-Cost and Agile Chip Fabrication IEEE Transactions on Very Large Scale Integration Systems (Accepted)

# A trial in 2024

• For Six students

whose major is not semiconductor

- Clean-room is used instead of the Minimal Fab in 2024.

- 1 day for design and 1 day for fabrication

- All designs worked well.

### Experimental Lab.

**Design with CAD**

**Etching**

Lithography Certification of the board

## Students can select one of three chips for bonding.

Worked at 143MHz: delay is 0.057ns

# Problems and future work

• Students just Observe During the Manufacturing Stage However, even just entering a cleanroom or handling the minimal-fab can have a significant impact on them.

## • We Currently Outsource Bonding to a Board Manufacturer.

- It needs a certain cost and time.

- Bonding machine is needed, but it is handled only by a skilled engineer.

- This Is Not a Full-Scale Semiconductor Design or Fabrication Exercise

- The RISC-V core and memory components are not utilized at all in the current setup.

- However, we are currently preparing a new digital IC fabrication experiment that incorporates these peripheral components.

- $\rightarrow$  Available on this July

Thank you for your listening

•Questions?